高密度 PCB 構造

高密度 IC により、高密度 PCB 設計者は、より小さなプレートにより多くの機能を持たせるための新しい設計戦略を見つける必要があります。 – エンドユーザー製品で – またはより大きな部品でより多くの機能.

集積回路上のより小さな要素の別の世代が進行中です. これは 65 nm範囲, しかし、一部のICメーカーはすでにプロトタイプを開発しています 45 nm要素. 現在生産されているICの最小素子, 約 90 nm, すでに接続の物理的基盤と競合しています.

印刷された接続, またはトラック, ディスクで信号の完全性とパフォーマンスの分布の問題が発生するまでは、小さくすることしかできません. 各プレートタイプへの新しいチップの組み立てには、いくつかの新しい戦略と過去に使用された戦略の両方が必要になります.

プリント回路基板の設計におけるこれらの問題は既知です: IC から信号を受信し、IC に送信する, シグナルインテグリティの維持, ディスクのコンポーネントに電力を分配する. 信号の完全性とは、クロストークを回避することを意味します, これは、トレースが互いに近すぎる場合に発生します, インピーダンスを管理して、非常に大きな高密度 PCB プレートで発生するため、長すぎるトラックで発生する可能性が高い信号反射を回避します。.

新しいコンプリケーションもあります: 非常に短い立ち上がり時間と立ち下がり時間. その後, 非常に短いトラックでも, 追加のインピーダンスの問題が発生する可能性があります.

5年前, テラビットのインターネットルーターはトップ製品だった. 含まれていた 52 PCB で、半分のラックまたは 3 足の高さ, 2 足の深さと 18 インチ幅. 現在、ルーターには PCB が 1 つしかなく、 1.5 高さインチ. 当時、1 つの IC に何十億ものトランジスタを搭載できると言われていたとしたら、 10 Gbps 対応トラック, 私たちは笑っただろう. サイズと速度の制限があるかどうかはわかりません.

小さな IC とトラックを備えたディスクのシグナル インテグリティの問題は、多くの場合、使い慣れた手法で処理できます。: トラックのサイズと分離を管理してクロストークを最小限に抑え、反射を避けるために適切な抵抗器でトラック接続を構築する. 1000分の1インチを最小トラック幅と見なします, そして 7 に 8 それらの間の最小距離として 1000 分の 1 インチ, チップのピン数に関係なく. 彼は 10000 分の 1 インチの間隔を好む.

新しい PCB アーキテクチャ

高密度 PCB の設計は 2 つの道を歩んできました. 1つは、非常に高密度のPCBにつながります, 携帯電話で使用される, デジタルカメラ, およびその他の民生用および家電機器, すべての回路がサムネイル サイズのボードに収まり、個々の充電間の耐用年数を延ばすために電力を控えめに分配する必要がある場合. もう 1 つは、スーパーコンピューターの高性能 PCB につながります。, 超高速ルーター, および類似のシステム.

これらの小さな PCB で, PCB 設計者は、限られたスペースにコンポーネントを詰め込む必要がありません, しかし、低電力要件でのパフォーマンスがすべてです. 大型の PCB は非常に高速で動作します. 2 種類の高密度ディスクには異なる問題があります, 設計者はより小さな要素で次世代の IC にスケールダウンします。.

IC を搭載した高性能ディスクの場合 1,000, 2,000, またはさらに多くのピン, 標準的な接続によって課せられる物理的な制限には、おそらく根本的に異なる設計手法が必要です.

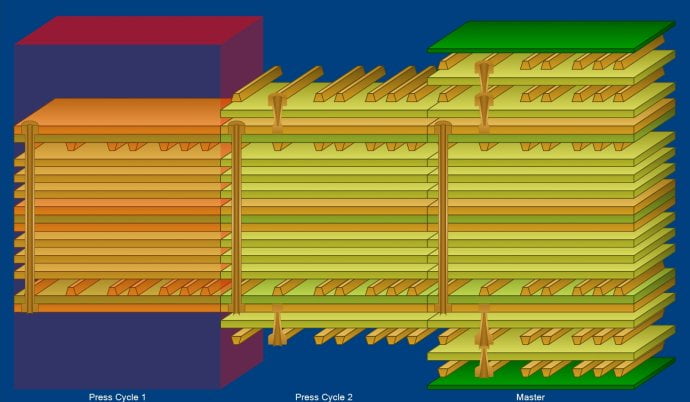

一例, 自称シグナルインテグリティエバンジェリスト, シグナルになる, オレーセにあります, カンザス, キューブ型の 3D PCB です。.

これは積み重ねられたレイヤーのコレクションではありません. 3Dならではの一体型デザインです, すべての重要なプロセスは、プロセッサの複数のレイヤーにわたって垂直に実行されます.

ラミネートに焦点を当てた他の技術. ラミネート素材を操作することで、信号損失を減らすことができます, 非常に薄いプレートは、より短くより多くの接続をサポートできます. 一部の新しい生産ラミネートは、 2 1000分の1インチの厚さと薄くなる. ボガティンによると, これらのラミネートにより、設計者は PCB のレイヤー数を半分に減らしながら、パフォーマンスの提供を向上させることができます。.

高密度 PCB の動作速度が 10 に 20 1980 年代の MHz から 21 世紀のギガビット/秒へ. 1980年代に, 目を閉じて皿をデザインできる. 次に、両目を大きく開く必要があります。”

シミュレーションとトレーニング

パネルがより複雑になり、製造業者は設計が不十分なために 1,500 ピンの IC を無駄にしたくありません。, シミュレーションとモデリングは PCB にとって重要です. 何かがうまくいかない場合, 適切なアクションを実行する必要があります, 実証済みの経験則ではうまくいかない. ディスクはますます ASIC に類似しています [特定用途向け集積回路], そして今、ICと同じタイプのシミュレーションがますます必要になっています. 一般的にこれを行うシミュレーション ツールが利用可能になりました, しかし、パフォーマンスの整合性ツールセットは今日でも不足しています.

超高密度PCB

MOKOテクノロジーは、テクノロジープラットフォームDencitecを示しています, これにより、高いスループットでプリント回路基板の機能を非常に高密度に統合できます。.

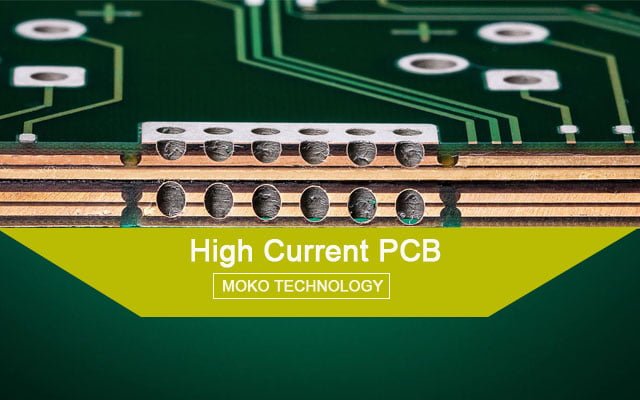

これらのオプションには、コンダクターと最大間隔の幅が含まれます。 25 μm の銅の厚さ 20 ±± 5 すべての導電層でμm, レーザービア径 35 μm, 直径の残留リング 30 内層のμmと 20 外層のμm, ビアスタッキングおよびパッド内ビアの可能性がある銅充填ブラインドビア. これにより、エネルギー供給などの追加オプションを統合するためのスペースが残ります (電池, 等). 加えて, 最新の材料が超薄型回路の製造を可能にします, 4 層フレックス回路など、総厚が 120 μm. 対照的に, 一般的に使用される標準的なプロセスは、導体の幅と間隔までは良好な結果しか得られません 50 μm および薄膜技術などの従来のセミアディティブ プロセスにより、導体の幅と間隔を 15 μm, ただし、一般的にはプロダクション フォーマットに限定されます.

PCB 製造におけるガルバニック銅析出のシミュレーション

を生産する前に、 高密度PCBボード, 受け取ったデータを慎重に分析します. これが、生産に対するすべての潜在的な影響を見つける方法です, 品質と長期的な信頼性を損なう可能性があります.

今まで, 電気めっきは、特定の設計がどのように動作するかを正確に判断できる人がほとんどいない分野です。. 回路基板に堆積される銅層の厚さは、レイアウト密度に依存します. 密度が低い場合, 過剰に構築するリスクがあります; 密度が高い場合, ビルドアップが少なすぎるリスクがあります. 強すぎる銅構造は、穴の中の穴が小さくなりすぎることを意味します. 低すぎる銅構造は、穴の壁が弱すぎることを意味します, メッキスルーホールが組み立て中に破損し、長期的な信頼性が失われる可能性があります.

目標は、回路基板全体にわたって均一な銅密度と均一な構造です. プリント回路基板を当社の製造ベネフィットに配置する際には、これを可能な限り考慮します。. 追加の銅パターンを配置できます (いわゆる補償面) 密度を補正するための回路基板間および回路基板の周囲. それにもかかわらず、, 回路基板の実際の設計を変更できないため、これらの方法に限定されます. 開発者のみがこれを行うことができます.

歴史的に, 銅密度を決定するための開発者ツールはありませんでした. 今日、MOKO Technologyは、プリント回路基板の色分けされた画像を使用したソリューションを提供しています, これは、銅の上部構造と下部構造の潜在的な領域を示しています.

ボードを小さなセルに分割する特別なガルバノ シミュレーション ソフトウェアを使用します。. 各セルの銅密度は、回路基板全体の平均銅密度と比較され、このセルに色が割り当てられます。. 平均よりも低い銅密度は、緑色からスケールで色付けされています (平均), 黄色とオレンジから赤. 赤くなるほど, 相対密度が低いほど、この領域に過剰な銅が蓄積するリスクが高くなります. 銅密度が高いセルは、緑から濃い青までのスケールで色付けされています. 青くなるほど, 銅の堆積が不十分になるリスクが高くなる.

このビジュアルデータを武器に, 開発者は、低密度領域に銅領域を追加したり、大きな銅領域を削減したりできます.

加えて, 回路基板上の銅密度の均一性を測定するガルバノ インデックスを提供します。. 完全に均一な回路基板の指数は 1. これは、電気メッキの問題が予想されないことを意味します. 値が低いほど均一性が低くなり、視覚化された画像で赤と青の領域で強調表示されます. 指数が下がった場合 0.8 以下, 特に注意が必要です. 上記の例では, ガルバノ指数は 0.65. ブルーエリア, 小さすぎる, はっきりと見ることができます.

ガルバノ画像は新規注文時に作成. このガルバノ写真は「PCB Image」の一部です, プリント回路基板のリアルな表現, 注文確認書と一緒にお送りします. 近い将来に, このシミュレーションは価格リクエスト機能の一部になります. いくつかのチェックを行い、それらからレポートを作成します. ガルバノ写真による, これも作成されました, 設計者は、高密度 PCB 回路基板の均一性を改善するために変更できるかどうかを確認できます。.

修正後, ガルバノ指数は 0.95. 写真は均一な銅の堆積を示しています.

ガルバノシミュレーション – 良いガルバノ インデックス層パターン – 良いガルバノインデックス

もちろん, 均一性の低い銅密度を避けられない設計上の制限がある場合があります。. このため, 完成したプリント回路基板の品質と信頼性を向上させる別のソリューションを準備中です. Elsyca Intellitool 陽極マトリックス プロジェクトは、最終的な銅構造の均一性をさらに向上させます.

複雑な電子機器向けのより高い実装密度

高密度 PCB ボードは、マイクロチップの進歩についていく必要があります。. 実装密度の高い回路は技術的飛躍を表す, これは、80年代半ばの表面実装への移行と同じくらい広範囲に影響を与えるはずです.

コンポーネントの漸進的な小型化, チップ, およびシステムは、今後数年間のプリント回路基板製造の劇的な技術的飛躍を意味するだけでなく、表面実装の導入によります。 (SMT) 80年代半ばに. マイクロチップの統合の成功は、接続技術も必要であることを意味するため、現在、ハイテク回路の分野で最も高い成長率が期待されています。. 課題は、集積密度の高いプリント回路基板用の最高級の構造を製造することです (高密度相互接続 – HDI) 経済的に.

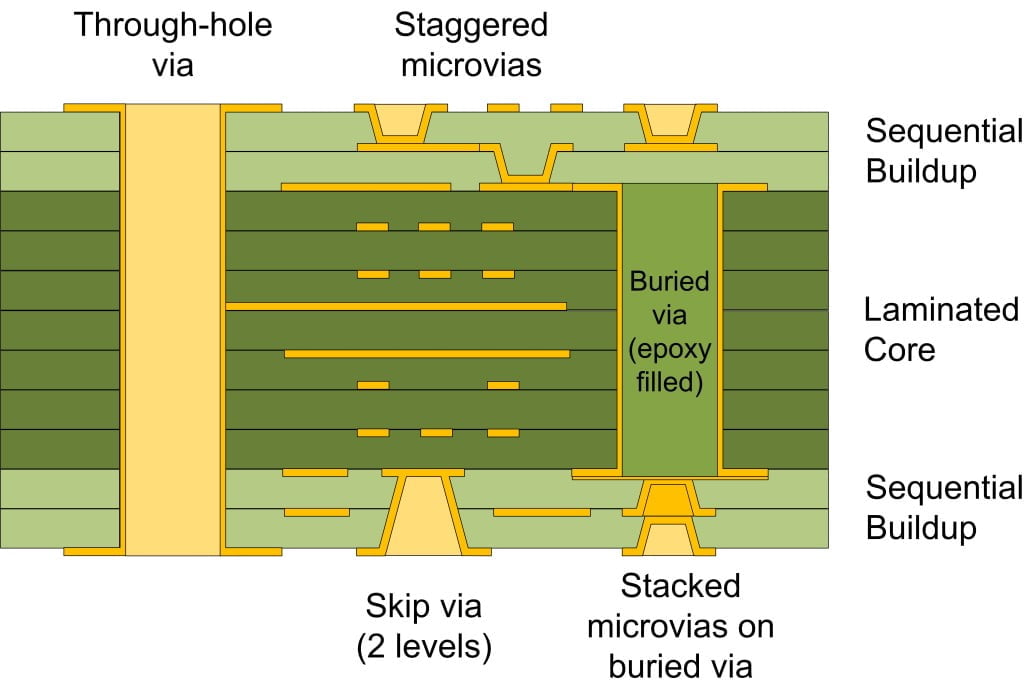

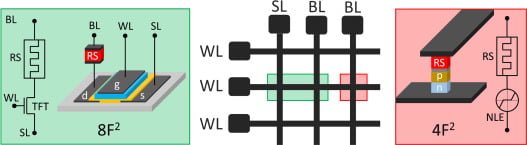

これまでのところ, 多極コンポーネントの接触の問題は、接続の一部を 1 つまたは複数の追加の信号層に移動することで解決されました。. しかしながら, 多層回路の製造 (多層) 比較的複雑であるため、コストがかかる. しかしながら, 一般に、層の数を減らすには、より微細な導体パターン構造を使用するか、穴の直径を小さくする必要があります。. 回路基板の個々の信号層を互いに電気的に接続するため, 導体トラックはいわゆるビアです, 私. ひ. ドリルで穴を開けてから金属化した穴, 次のレベルまたはプレートの下側につながった. プリント回路基板には数千の穴がある場合があるため、, 穴の直径を小さくするだけで大幅な節約の可能性があります. 機械的に, しかしながら, このような微細な穴 (マイクロウェイ) 以下の直径で 0.1 mm はレーザーでしか製造できない, 従来の掘削では 0.2 mmが限界に達する.

しかしながら, マイクロ ビアは、細線構造化におけるさらに複雑な回路への第一歩にすぎません。. ここで特に重要な作業ステップには、写真プロセス全体が含まれます, その助けを借りて、回路基板基材の銅被覆は通常構造化されています. 超微細導体技術は、露光とその後のエッチングステップに特に高い要求を課します. 幅と間隔が以下の構造の場合 0.1 mm は連続生産で実現されます, 場合によっては生産歩留まりが劇的に低下する. これは、写真プロセス全体を大幅に簡素化する新しい制作方法によって改善できます。. これには直接レーザー照射が含まれます, 導体パターンで直接フォトレジストを記述する. 従来のフィルムを使った露光工程を一切省略.

技術的に, 直接暴露は、ロットサイズに関して柔軟性が高く、構造分解能が高いため、以前の接触暴露よりも優れています。. したがって、プロセスステップの数を大幅に削減できます. クリーンルームのランニングコスト, フィルムとマスク, フォトレジスト、および環境に有害な材料と残留物の廃棄にかかる費用も、この手順で削減されます. レーザービームのコヒーレンスが高いため、最小限の放射線不足で最小構造の信頼性の高いイメージングが可能になるため、特に非常に細い導体で高い歩留まりを達成できます。. 直接イメージセッターの被写界深度が深いため, 高低差もある程度補正可能. 付加機能として、自動光学パネル測定や個別使用インジケータも考えられます。. レーザー ダイレクト ストラクチャリングがさらに簡単に, レーザーが導体パターンを銅被覆に直接加工する方法, これは、レジストが不要であることを意味します。.

中国企業は、新しい接続技術の開発でもリーダーです. “MOV” カールスルーエ社のインボードは新しいコンセプトで、多層表面配線の略です。. この新しいタイプの高密度 PCB 回路基板は、 “一体型回路基板” 抵抗やコンデンサなどの電子部品が回路基板に組み込まれているため.

集積回路基板は、より微細な導体トラック構造とレーザーでドリル加工されたブラインド ホールを提供するだけではありません。 80 導体トラックに接続するための直径 µm, しかし、電気データも印象的です. 従来の多層配線との比較, 同じ機能のケーブル長は 35%. すべての層を通るビアの数は、 80%, 参照例の信号層の数が 6 から 2 に.

でも、また一方的な組み立て技術でやり遂げることが重要です. 抵抗器とコンデンサーは次のように含めることができます。 “印刷” コンポーネント. この新しい開発は、動作周波数に対する要求の高まりによって引き起こされました, コンポーネント接続の数と、ボール グリッド アレイやチップ サイズ パッケージなどの小型設計. 例えば, と 50 プリント回路基板上のプリント抵抗器, SMD アセンブリよりもコスト面で有利です。, 船内によると.

私たちは、光データ伝送のための費用対効果の高いソリューションに取り組んでいます. プラスチック製の帯状光ファイバ, いわゆるバックプレーンに取り付けられる, 非常に平らな方法でコンピュータのハードウェア コンポーネントを接続します, までの導光性プラスチックストリップ 50 長さセンチ. ストリップ導波路の新しい製造プロセスは、あらゆるキャリア材料に適しています, 特にプリント基板材料用. 私たちは異なるアプローチを取り、ホットスタンプによって製造された光導体を特別な回路基板層に統合します. これにより、ブランチなどのパッシブ光コンポーネントを実装できます, 電気回路基板技術に類似した光配線を可能にする. 回路基板は単純な接続要素から複雑なアセンブリへと進化しています.