Leiterplattenkonstruktion mit hoher Dichte

ICs mit hoher Dichte zwingen Leiterplattenentwickler mit hoher Dichte, neue Designstrategien zu finden, um entweder mehr Funktionalität auf kleineren Platten zu haben – in Endbenutzerprodukten – oder viel mehr Funktion bei größeren Teilen.

Eine weitere Generation kleinerer Elemente in integrierten Schaltkreisen ist unterwegs. Das ist in der 65 nm Bereich, Einige IC-Hersteller entwickeln jedoch bereits Prototypen mit 45 nm Elemente. Die kleinsten Elemente in derzeit produzierten ICs, Über 90 nm, bereits in Konflikt mit der physischen Basis der Verbindung.

Gedruckte Verbindungen, oder Spuren, kann nur klein sein, bis auf der Festplatte Probleme mit der Signalintegrität und der Leistungsverteilung auftreten. Die Montage der neuen Chips auf jedem Plattentyp erfordert sowohl einige neue als auch die in der Vergangenheit verwendeten Strategien.

Diese Probleme bei der Konstruktion von Leiterplatten sind bekannt: Empfangen von Signalen von ICs und Senden dieser an ICs, Aufrechterhaltung der Signalintegrität, und Verteilen von Energie auf die Komponenten der Platte. Signalintegrität bedeutet, Übersprechen zu vermeiden, Dies tritt auf, wenn die Spuren zu nahe beieinander liegen, und Verwalten der Impedanz, um Signalreflexionen zu vermeiden, die eher in einer zu langen Spur auftreten, weil sie auf sehr großen Leiterplatten mit hoher Dichte auftreten.

Es gibt auch eine neue Komplikation: sehr kurze Anstiegs- und Abfallzeiten. Dann, auch bei sehr kurzen spuren, Möglicherweise können zusätzliche Impedanzprobleme auftreten.

Vor fünf Jahren, Ein Terabit-Internet-Router war ein Top-Produkt. Es enthielt 52 PCBs und war ein halbes Rack oder 3 Fuss hoch, 2 Füße tief und 18 Zoll breit. Jetzt hat der Router nur noch eine Platine und ist nur noch 1.5 Zoll hoch. Wenn uns damals gesagt worden wäre, dass ein IC Milliarden von Transistoren aufnehmen könnte und 10 Gbit / s-kompatible Tracks, wir hätten gelacht. Jetzt weiß ich nicht, ob es überhaupt Größen- und Geschwindigkeitsbegrenzungen gibt.

Die Signalintegritätsprobleme auf Festplatten mit kleineren ICs und Spuren können häufig mit bekannten Techniken behandelt werden: Verwalten der Spurgröße und -trennung zur Minimierung des Übersprechens und Aufbau von Spurverbindungen mit geeigneten Widerständen, um Reflexionen zu vermeiden. Wir betrachten Tausendstel Zoll als minimale Spurbreite, und 7 zu 8 Tausendstel Zoll als Mindestabstand zwischen ihnen, egal wie viele Pins ein Chip hat. Er bevorzugt einen Abstand von 10 Tausendstel Zoll.

Neue PCB-Architekturen

Das Design von Leiterplatten mit hoher Dichte hat zwei Wege eingeschlagen. Man führt zu den Leiterplatten, die wirklich eine hohe Dichte haben, in Mobiltelefonen verwendet, Digitalkameras, und andere Geräte für die Verbraucher- und Heimelektronik, Wenn alle Schaltkreise auf eine Platine mit Daumennagelgröße passen, muss die Leistung sparsam verteilt werden, um die Lebensdauer zwischen den einzelnen Ladungen zu verlängern. Der andere führt zu Hochleistungsplatinen in Supercomputern, extrem schnelle Router, und ähnliche Systeme.

Auf diesen winzigen Leiterplatten, Leiterplattenentwickler müssen keine Komponenten auf engstem Raum zusammendrücken, Leistung bei geringem Strombedarf ist jedoch alles. Größere Leiterplatten arbeiten mit sehr hohen Geschwindigkeiten. Die beiden Arten von Festplatten mit hoher Dichte haben unterschiedliche Probleme, Während Designer mit kleineren Elementen auf die nächste Generation von ICs verkleinern.

Für Hochleistungsfestplatten mit ICs, die haben 1,000, 2,000, oder noch mehr Stifte, Die durch Standardverbindungen auferlegten physikalischen Grenzen erfordern wahrscheinlich radikal unterschiedliche Entwurfstechniken.

Ein Beispiel, ein selbsternannter Evangelist für Signalintegrität, dessen Gesellschaft, sei das Signal, befindet sich in Olathe, Kansas, ist eine würfelförmige 3-D-Leiterplatte.

Dies ist keine Sammlung gestapelter Ebenen. Es ist ein integriertes Design, das spezifisch für 3D ist, Dabei laufen alle wichtigen Prozesse vertikal über mehrere Prozessorebenen.

Andere Techniken konzentrieren sich auf Laminate. Die Manipulation von Laminatmaterial kann dazu beitragen, den Signalverlust zu verringern, und sehr dünne Platten können kürzere und mehr Verbindungen unterstützen. Einige neue Produktionslaminate sind nur 2 Tausendstel Zoll dick und dünner werden. Laut Bogatin, Mit diesen Laminaten können Entwickler die Anzahl der Schichten auf einer Leiterplatte halbieren und gleichzeitig die Leistungsbereitstellung verbessern.

Die Betriebsgeschwindigkeiten von Leiterplatten mit hoher Dichte wurden von erhöht 10 zu 20 MHz in den 1980er Jahren auf Gigabit pro Sekunde im 21. Jahrhundert. In den 1980er Jahren, Sie könnten einen Teller mit geschlossenen Augen entwerfen. Jetzt müssen Sie beide Augen weit öffnen.”

Simulation und Training

Da die Panels immer komplexer werden und ihre Hersteller aufgrund des schlechten Designs keine 1.500-Pin-ICs verschwenden möchten, Simulation und Modellierung sind für Leiterplatten von entscheidender Bedeutung. Wenn etwas nicht funktioniert, Sie müssen qualifizierte Maßnahmen ergreifen, und Sie können mit bewährten Faustregeln nicht weitermachen. Festplatten ähneln zunehmend ASICs [Anwendungsspezifische integrierte Schaltkreise], und jetzt brauchen wir zunehmend die gleiche Art von Simulation wie für ICs. Simulationswerkzeuge, die dies im Allgemeinen tun, sind jetzt verfügbar, Toolsets für die Leistungsintegrität fehlen jedoch noch heute.

Extrem hochdichte Leiterplatte

MOKO Technology zeigt die Technologieplattform Dencitec, Dies ermöglicht eine extrem hohe Dichte an integrierten Funktionen für Leiterplatten mit hohem Durchsatz.

Diese Optionen umfassen Leiter- und Abstandsbreiten von bis zu 25 μm mit Kupferdicken von 20 ± 5 μm auf allen leitenden Schichten, Laser über Durchmesser von 35 μm, Restringe mit einem Durchmesser von 30 μm auf den inneren Schichten und 20 μm auf den äußeren Schichten, kupfergefüllte Blinddurchkontaktierungen mit der Möglichkeit der Durchkontaktierung und Durchkontaktierungen in Pads. Dies lässt mehr Raum für die Integration zusätzlicher Optionen wie der Energieversorgung (Batterien, usw.). Zusätzlich, Moderne Materialien ermöglichen die Herstellung ultradünner Schaltungen, wie vierschichtige Flexschaltungen mit einer Gesamtdicke von weniger als 120 μm. Im Gegensatz, Üblicherweise verwendete Standardverfahren liefern nur bis zu Leiterbreiten und -abständen von gute Ergebnisse 50 μm und klassische semi-additive Verfahren wie die Dünnschichttechnologie ermöglichen Leiterbreiten und -abstände von weniger als 15 μm, sind aber in der Regel auf Produktionsformate beschränkt.

Eine Simulation der galvanischen Kupferabscheidung in der Leiterplattenfertigung

Bevor wir ein produzieren Leiterplatte mit hoher Dichte, Wir analysieren die erhaltenen Daten sorgfältig. So finden wir alle möglichen Auswirkungen auf die Produktion, Dies könnte die Qualität und die langfristige Zuverlässigkeit beeinträchtigen.

Bis jetzt, Das Galvanisieren war ein Bereich, in dem kaum jemand genau bestimmen konnte, wie sich ein bestimmtes Design verhalten wird. Die Kupferschichtdicke, die auf der Leiterplatte abgeschieden wird, hängt von der Layoutdichte ab. Wenn die Dichte niedrig ist, Wir riskieren zu viel zu bauen; wenn die Dichte hoch ist, Wir riskieren zu wenig Aufbau. Eine zu starke Kupferstruktur führt dazu, dass die Löcher in den Löchern zu klein werden. Eine zu niedrige Kupferstruktur bedeutet, dass die Lochwände zu schwach sind, so dass die durchkontaktierten Löcher während der Montage brechen und ihre langfristige Zuverlässigkeit verlieren können.

Ziel ist eine gleichmäßige Kupferdichte und eine gleichmäßige Struktur über die gesamte Leiterplatte. Dies berücksichtigen wir so weit wie möglich, wenn wir die Leiterplatten auf unsere Produktionsvorteile setzen. Wir können zusätzliche Kupfermuster platzieren (sogenannte Kompensationsflächen) zwischen und um die Leiterplatte, um die Dichte zu kompensieren. Dennoch, Wir sind auf diese Methoden beschränkt, da wir das tatsächliche Design der Leiterplatte nicht ändern können. Dies kann nur der Entwickler.

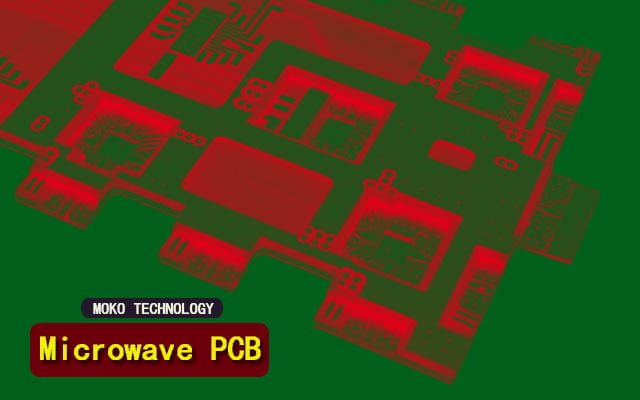

Historisch, Es gab keine Entwicklerwerkzeuge zur Bestimmung der Kupferdichte. Heute bietet MOKO Technology eine Lösung mit einem farbcodierten Bild der Leiterplatte, Dies zeigt die potenziellen Bereiche des Aufbaus und der Unterkonstruktion von Kupfer.

Wir verwenden eine spezielle Galvano-Simulationssoftware, die die Platine in kleine Zellen unterteilt. Die Kupferdichte jeder Zelle wird mit der durchschnittlichen Kupferdichte der gesamten Leiterplatte verglichen, und dieser Zelle wird dann die Farbe zugewiesen. Eine unterdurchschnittliche Kupferdichte wird auf einer Skala von grün gefärbt (durchschnittlich), gelb und orange bis rot. Je roter, Je geringer die relative Dichte und je höher das Risiko einer übermäßigen Kupferbildung in diesem Bereich ist. Zellen mit einer höheren Kupferdichte sind auf einer Skala von grün bis dunkelblau gefärbt. Je mehr blau, Je größer das Risiko einer unzureichenden Kupferbildung.

Mit diesen visuellen Daten bewaffnet, Der Entwickler kann Kupferbereiche in Bereichen mit geringer Dichte hinzufügen oder große Kupferbereiche reduzieren.

Zusätzlich, Wir werden einen Galvano-Index bereitstellen, der die Gleichmäßigkeit der Kupferdichte auf der Leiterplatte misst. Eine völlig gleichmäßige Leiterplatte hat einen Index von 1. Dies bedeutet, dass keine Galvanikprobleme zu erwarten sind. Niedrigere Werte zeigen eine geringere Gleichmäßigkeit und werden auf dem visualisierten Bild durch rote und blaue Bereiche hervorgehoben. Wenn der Index auf fällt 0.8 oder weniger, Besondere Aufmerksamkeit ist erforderlich. In dem oben gezeigten Beispiel, Der Galvano-Index ist 0.65. Der blaue Bereich, das ist zu klein, ist deutlich zu sehen.

Das Galvano-Bild wird erstellt, wenn eine neue Bestellung aufgegeben wird. Dieses Galvano-Bild ist Teil von „PCB Image“., eine realistische Darstellung Ihrer Leiterplatten, die wir Ihnen zusammen mit der Auftragsbestätigung zusenden. In naher Zukunft, Diese Simulation wird Teil der Preisanforderungsfunktion. Wir werden eine Reihe von Überprüfungen durchführen und daraus einen Bericht erstellen. Basierend auf dem Galvano-Bild, welches auch geschaffen wurde, Der Konstrukteur kann sehen, ob er Änderungen vornehmen kann, um die Gleichmäßigkeit seiner Leiterplatte mit hoher Dichte zu verbessern.

Nach der Änderung, Der Galvano-Index ist 0.95. Das Bild zeigt eine gleichmäßige Kupferabscheidung.

Galvano-Simulation – gutes Galvano-Index-Schichtmuster – guter Galvano Index

Natürlich, Es kann Konstruktionsbeschränkungen geben, die eine weniger gleichmäßige Kupferdichte unvermeidbar machen. Dafür, Wir bereiten eine weitere Lösung vor, um die Qualität und Zuverlässigkeit der fertigen Leiterplatte zu verbessern. Das Anodenmatrixprojekt Elsyca Intellitool wird die Gleichmäßigkeit der endgültigen Kupferstruktur weiter verbessern.

Mehr Packungsdichte für komplexe Elektronik

Die hochdichten Leiterplatten müssen mit den Fortschritten bei Mikrochips Schritt halten. Schaltungen mit einer hohen Packungsdichte stellen einen Technologiesprung dar, Dies dürfte ebenso weitreichende Konsequenzen haben wie der Übergang zur Aufputzmontage Mitte der achtziger Jahre.

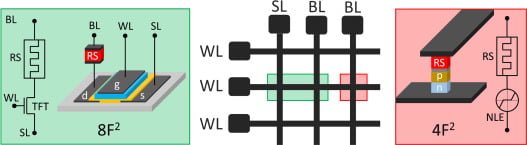

Fortschreitende Miniaturisierung von Bauteilen, Chips, und Systeme werden in den kommenden Jahren sowie aufgrund der Einführung der Oberflächenmontage einen drastischen Technologiesprung für die Herstellung von Leiterplatten bedeuten (SMT) Mitte der achtziger Jahre. Die höchsten Wachstumsraten sind derzeit im Bereich der High-Tech-Schaltungen zu erwarten, da aufgrund des Integrationserfolgs der Mikrochips auch die Verbindungstechnik erforderlich ist. Die Herausforderung besteht darin, feinste Strukturen für Leiterplatten mit hoher Integrationsdichte herzustellen (Verbindung mit hoher Dichte – HDI) wirtschaftlich.

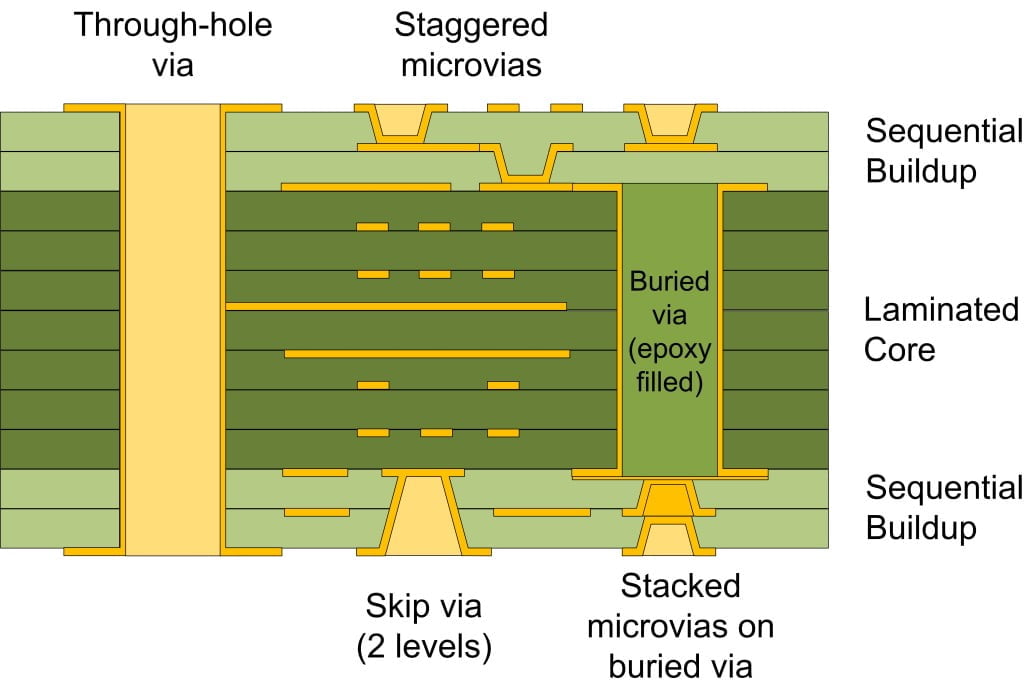

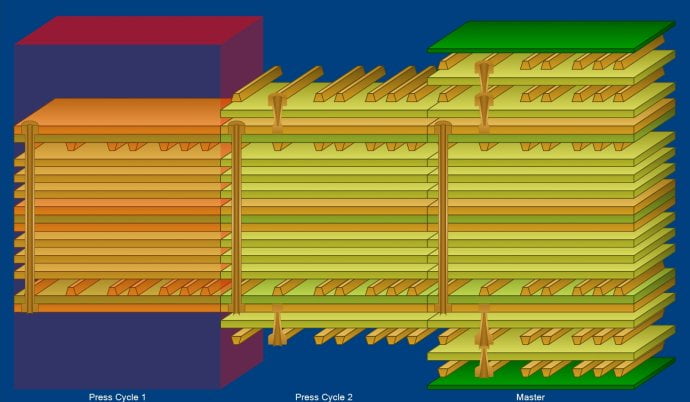

Bisher, Die Kontaktprobleme mit mehrpoligen Komponenten wurden gelöst, indem einige der Verbindungen auf eine oder mehrere zusätzliche Signalschichten verschoben wurden. jedoch, die Herstellung von mehrschichtigen Schaltungen (mehrschichtig) ist vergleichsweise komplex und daher teuer. jedoch, Die Anzahl der Schichten kann im Allgemeinen nur durch Verwendung feinerer Leitermusterstrukturen oder durch Verwendung kleinerer Lochdurchmesser verringert werden. Um die einzelnen Signalschichten der Leiterplatte elektronisch miteinander zu verbinden, Die Dirigentenbahnen sind sogenannte Durchkontaktierungen, ich. H.. gebohrte und dann metallisierte Löcher, führte zur nächsten Ebene oder zur Unterseite der Platte. Da eine Leiterplatte mehrere tausend Löcher haben kann, Allein durch die Reduzierung des Lochdurchmessers besteht ein enormes Einsparpotenzial. Mechanisch, jedoch, solche Mikrolöcher (Mikro Wege) mit einem Durchmesser von weniger als 0.1 mm kann nur mit Lasern hergestellt werden, während traditionelle Bohrungen bei 0.2 mm stößt an seine Grenzen.

jedoch, Mikro-Vias sind nur der erste Schritt zu noch komplexeren Schaltkreisen bei der Feindrahtstrukturierung. Die besonders kritischen Arbeitsschritte umfassen hier den gesamten Fotoprozess, mit deren Hilfe üblicherweise die Kupferummantelung des Leiterplattengrundmaterials strukturiert wird. Die Feinstleitertechnologie stellt besonders hohe Anforderungen an die Belichtung und den anschließenden Ätzschritt. Wenn Strukturen mit einer Breite und einem Abstand von weniger als 0.1 mm sind in Serie zu realisieren, In einigen Fällen sinkt die Produktionsausbeute dramatisch. Dies kann durch neue Produktionsmethoden behoben werden, die den gesamten Fotoprozess erheblich vereinfachen. Dies schließt eine direkte Laserbelichtung ein, welches den Fotolack direkt mit dem Leitermuster beschreibt. Der herkömmliche Belichtungsschritt unter Verwendung eines Films entfällt vollständig.

Technisch, Die direkte Belichtung ist der vorherigen Kontaktbelichtung überlegen, da sie mehr Flexibilität hinsichtlich der Losgrößen und eine höhere Strukturauflösung bietet. Die Anzahl der Prozessschritte kann somit erheblich reduziert werden. Laufende Kosten für Reinraum, Filme und Masken, Mit diesem Verfahren werden auch Fotolacke sowie die daraus resultierenden Kosten für die Entsorgung umweltschädlicher Materialien und Rückstände reduziert. Insbesondere bei sehr feinen Leitern können höhere Ausbeuten erzielt werden, da die hohe Kohärenz des Laserstrahls eine zuverlässige Abbildung der kleinsten Strukturen bei minimaler Unterstrahlung ermöglicht. Und aufgrund der höheren Schärfentiefe des direkten Belichters, Auch Höhenunterschiede können bis zu einem gewissen Grad ausgeglichen werden. Als zusätzliche Funktionen sind auch eine automatische optische Panelmessung und individuelle Nutzungsanzeigen denkbar. Die direkte Laserstrukturierung ist noch einfacher, bei dem der Laser das Leitermuster direkt in die Kupferummantelung fräst, Dies bedeutet, dass kein Resist mehr benötigt wird.

Chinesische Unternehmen sind auch führend bei der Entwicklung neuer Verbindungstechnologien. “MOV” von der Karlsruher Firma Inboard ist ein neues Konzept und steht für mehrschichtige Oberflächenverdrahtung. Dieser neue Typ einer Leiterplatte mit hoher Dichte wird auch als bezeichnet “integrierte Leiterplatte” weil elektronische Komponenten wie Widerstände und Kondensatoren in die Leiterplatte integriert sind.

Die integrierte Leiterplatte bietet nicht nur feinere Leiterbahnstrukturen und lasergebohrte Sacklöcher von weniger als 80 µm Durchmesser zum Kontaktieren der Leiterbahnen, Aber auch die elektrischen Daten sind beeindruckend. Im Vergleich zu herkömmlichen Mehrschichtverdrahtungen, Die Kabellänge bei gleicher Funktion wird um reduziert 35%. Die Anzahl der Durchkontaktierungen durch alle Ebenen wird sogar um reduziert 80%, die Anzahl der Signalschichten in einem Referenzbeispiel von sechs bis nur zwei.

Es ist jedoch wichtig, dass Sie wieder mit einseitiger Montagetechnologie auskommen. Widerstände und Kondensatoren können als enthalten sein “gedruckt” Komponenten. Auslöser dieser Neuentwicklung waren die steigenden Anforderungen an die Arbeitsfrequenz, die Anzahl der Komponentenanschlüsse und immer kleinerer Designs wie Ball Grid Array und Chip Size Packaging. Zum Beispiel, mit 50 gedruckte Widerstände auf einer Leiterplatte, Es gibt einen Kostenvorteil gegenüber der SMD-Montage, nach dem Innenborder.

Wir arbeiten an kostengünstigen Lösungen für die optische Datenübertragung. Eine streifenförmige Lichtleitfaser aus Kunststoff, welches an eine sogenannte Rückwandplatine angeschlossen ist, verbindet Hardwarekomponenten im Computer über sehr flach, lichtleitende Kunststoffstreifen von bis zu 50 cm lang. Das neuartige Herstellungsverfahren für den Streifenwellenleiter ist für alle Trägermaterialien geeignet, insbesondere für Leiterplattenmaterial. Wir verfolgen einen anderen Ansatz und integrieren die durch Heißprägen erzeugten optischen Leiter in spezielle Leiterplattenschichten. Dadurch können passive optische Komponenten wie Zweige implementiert werden, die eine optische Verdrahtung analog zur Leiterplattentechnologie ermöglichen. Die Leiterplatte entwickelt sich von einem einfachen Verbindungselement zu einer komplexen Baugruppe.