Moderne elektrische und elektronische Produkte und Komponenten zeichnen sich durch modernste Technologien aus und bieten Anwendern Funktionen und Dienstleistungen, die noch vor wenigen Jahren undenkbar waren. Aber trotz modernster Technik und Fertigung, Fehler und Ausfälle von elektrischen und elektronischen Produkten und Komponenten treten in der Praxis immer wieder auf, das brachte uns zum heutigen Thema: PCB-Fehleranalyse!

Die Gründe dafür sind vielfältig und reichen von unzureichendem Design über schlechte Materialqualität bis hin zu ungenauen Herstellungsspezifikationen. Unglücklicherweise, jedoch, Fehler und Ausfälle bei elektrischen und elektronischen Produkten sind oft nicht nur eine Unannehmlichkeit, sondern können auch mit erheblichen Risiken für Mensch und Umwelt einhergehen.

Was ist eine PCB-Fehleranalyse?

Der Begriff PCB-Fehleranalyse steht für eine umfassende Untersuchung der Ursachen, die zum Ausfall eines Produkts oder einer Komponente geführt haben. Verwendung einer Vielzahl von Techniken und Testmethoden, Testingenieure identifizieren und bewerten die spezifischen Ursachen für den Ausfall eines Produkts oder einer Komponente.

Sobald die Ursache festgestellt ist, Es können Maßnahmen ergriffen werden, um das Produkt zu modifizieren oder neu zu entwickeln, um künftige Produktfehler zu vermeiden. Einige Fehleranalysemethoden können auch in der Prototypenphase verwendet werden, um potenzielle Fehler frühzeitig zu erkennen und Schwachstellen zu beheben, bevor ein Produkt auf den Markt gebracht wird.

Warum ist die Analyse von Leiterplattenfehlern wichtig?

Produktausfälle haben eine Reihe von Konsequenzen für Hersteller von elektrischen und elektronischen Produkten und Komponenten. Produkte, die nicht wie versprochen funktionieren, können zu enttäuschten Benutzern führen und den Ruf eines Unternehmens als Hersteller hochwertiger Produkte schädigen. jedoch, Produktfehler können auch zu kostspieligen und zeitaufwändigen Produktrückrufen und der damit verbundenen negativen Publizität führen.

Im schlimmsten Fall, Produktfehler gefährden Menschen und Sachwerte und verursachen Verletzungen oder sogar den Tod. Die Fehleranalyse hilft Herstellern, die Qualität und Sicherheit ihrer Produkte zu verbessern und das Risiko zukünftiger Ausfälle bei ähnlichen Geräten zu verringern.

Was kann die MOKO-Technologie für Ihre Leiterplatte tun?

Zur Fehleranalyse, Wir bieten die gesamte Palette von Prüfdienstleistungen für elektrische und elektronische Produkte und Komponenten an. Neben der Fehleranalyse, Wir bieten auch die folgenden Testservices an:

Beschichtungstests / Dünnschichttechnologie

- einschließlich der Bestimmung der chemischen Zusammensetzung, Schichtdicke, Orientierung und Qualität der Beschichtung sowie Adhäsionstests.

Testen von Leiterplatten - z. Bestimmung der Dicke und Homogenität der Verzinkungsschicht, Delaminierungsprüfungen und Prüfung der Lötmittelbeständigkeit

Produkttest

- z.B. Strahlungstests zur Bestimmung des baulichen Zustands oder zur Feststellung innerer Defekte, elektrische Charakterisierung durch Kurventest, Dye-and-Pry-Test in einem Kugelgitter-Array (BGA) und Verbindungen, und Untersuchung der Lötbarkeit.

Zuverlässigkeits- und Betriebssicherheitstests, einschließlich Untersuchungen nach Temperaturänderungen und Schockprüfungen, Feuchtigkeitstests und Salznebeltests.

Oberflächenanalyse

– Röntgenphotoelektronenspektroskopie (XPS) und Rasterkraftmikroskopie (AFM) und andere Methoden

Thermische Analyse mittels Differential Scanning Calorimetry (DSC), Thermogravimetrische Analyse (TGA) und thermomechanische Analyse (DUNKEL) und andere Methoden.

Chemische Analyse

- einschließlich Massenspektrometrie mit induktiv gekoppeltem Plasma (ICP-MS), Fourier-Transformations-Infrarotspektroskopie (FTIR) und Gaschromatographie mit Massenspektrometriekopplung (GC-MS).

Mechanische Prüfungen, einschließlich Zugversuchen, Ermüdungs- und Vibrationstests.

Elektromagnetische Verträglichkeitsprüfungen (EMV)

– in Bezug auf Leitungs- und Strahlungsemissionen sowie Immunität.

Risse in der Metallisierung von Leiterplatten

Problem: Elektronikmodul ausgefallen

Lösung: Metallographischer Querschnitt

Ergebnis: Risse in der Metallisierung

Flip-Chip-Kontakte

Beispiel aus Project HTM

Flip-Chip-Kontakte nach Öltest,

13346, NiAu / SbSn / PdAg,

2000 h bei 200 ° C.

Ablagerungen auf Leiterplatten

Untersuchung von Einlagen

Methoden: FTIR-Ergebnisse:

Carboxylate (Salze von Carbonsäuren,

speziell Adipinsäure (Hexansäure) und IC

Untersuchung von Einlagen

Methode: REM und EDX

Bondabliftber

Fehleranalyse von mehrschichtigen Leiterplatten

Problem: Ein Sensor auf einer Leiterplatte thermisch belastet keinen elektrischen Kontakt mehr

Lösung: Metallographischer Querschnitt

Ergebnis: Ein Wedge-Bond-Kontakt wurde aufgehoben

Ursache: Risse zwischen Leiterplatte und Gloptop führten zu mechanischer Beanspruchung.

Kontamination

Beschreibung:

Verunreinigungen und Korrosion auf der Kupferoberfläche verursachten Probleme beim Verzinnen dieses Lötauges. Zusätzlich, Mängel (helle Bereiche) sind auf der Kupferoberfläche sichtbar, auf dem das Grundmaterial durchscheint (Die Schichtdicke des Kupfers ist zu dünn). Inakzeptabler Fehler, da im späteren Lötprozess kein Löten auftreten kann.

Ursachen / Abhilfemaßnahmen:

• Elektrischer Herstellungsfehler des Herstellers

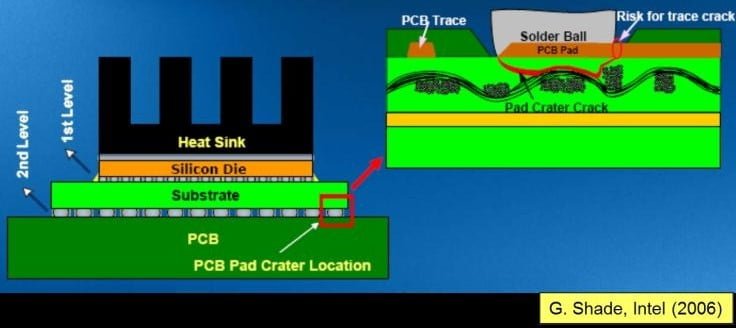

Der Krater auf einer Komponente

Goldschicht

Beschreibung:

Fehler im Galvanikprozess. An den markierten Stellen, zu wenig Gold wurde galvanisch abgelagert. Die darunter liegende Schicht (Ni) zeigt die ersten Anzeichen von Korrosion. Unerträglicher Fehler, als Lötfehler, kann beim Löten auftreten.

Ursachen / Abhilfemaßnahmen:

• Galvanikprozess mangelhaft

• Vorbereitung der Leiterplatte (Reinigung, Unterlagen) mangelhaft

Goldschicht defekt

Knotenbildung

Beschreibung:

Knotenbildung der Ni-Barrier-Schicht unter der Goldoberfläche. Aufgrund ungünstiger Stromverteilung im Galvanikprozess, In der mittleren Schicht bildeten sich viele Knötchen (siehe unteres Bild, Schnitt) das ragen durch die Goldschicht. In der Übersicht, Diese Knötchen sind deutlich sichtbar. Diese Leiterplatte sollte nicht verwendet werden, da Löt- oder Kontaktprobleme zu erwarten sind.

Ursachen / Abhilfemaßnahmen:

Die mittlere Ni-Schicht des Galvanisierungsprozesses bricht durch die obere Goldschicht

Knotenbildung

Unterbrechung

Beschreibung:

Unterbrechung einer Spur. Aufgrund von Fehlern im galvanischen Prozess bei der Herstellung der Leiterplatte (subtraktiver Prozess), Ein Teil der Spur wurde weggeätzt. Dieser Fehler ist ein Hinweis auf Fehler im Fotolack. Herstellungsfehler.

Galvanikfehler bei der Herstellung der Leiterplatte

Fehler im Fotolack / Prozessfehler des Herstellers

Teilunterbrechung

Beschreibung:

Gleiche Verbindung wie oben gezeigt, jedoch, Die Spur ist nicht vollständig getrennt. Obwohl die elektrische Funktion gegeben ist, Probleme mit der Funktion der Leiterplatte können später unter elektrischen Lastbedingungen auftreten.

Galvanikfehler in Leiterplattenherstellung

Fehler im Fotolack / Prozessfehler des Herstellers

Teilweise Unterbrechung der Spur eines Dirigenten

Einschluss von Fremdpartikeln

Beschreibung:

Einschluss eines Fremdpartikels in Spuren. Dies ist wahrscheinlich Glasfaser des Grundmaterials. Weil dieser Einschluss die Spurdicke reduziert, Dieser Fehler ist nicht akzeptabel.

Ursachen / Abhilfemaßnahmen:

Fehler bei der Herstellung der Leiterplatte

Unebene Lackoberfläche

Ursachen / Abhilfemaßnahmen:

• Abdeckmaske ungeeignet

• Verschmutzung der Oberflächen der Leiterplatte

• Wärmebelastung des Lackes mangelhaft

Ursachen / Abhilfemaßnahmen:

• Fehler im Beschichtungsprozess der Farbe

• Ablösen des Lackmangels

Beschreibung:

Der Versatz der Beschichtung gegenüber ihrer idealen Position. Dieser häufigste Fehler hat einen sehr großen Einfluss auf die spätere Lötqualität, weil (wie im Bild gezeigt) Die benetzbaren Oberflächen können erheblich reduziert oder vollständig verdeckt werden. Unerträglicher Fehler.

Der Versatz der Deckbeschichtung

Beschreibung:

Der Versatz der Beschichtung gegenüber ihrer idealen Position.

Ursachen / Abhilfemaßnahmen:

Fehler im Beschichtungsprozess der Farbe

Lackentfernung mangelhaft

Fehler im Zusammenhang mit dem Layout (Exposition)

Aufnahme

Beschreibung:

Einschluss von undefinierten Partikeln unter die Farbe. Kurzschlüsse (elektrisch leitende Einschlüsse) wird durch diesen Fehler verursacht.

Ursachen / Abhilfemaßnahmen:

Herstellungsfehler des Herstellers

Verunreinigung des unbeschichteten Grundmaterials

Mängel

Beschreibung:

Teilfehler in der Beschichtung, die unregelmäßige Schichtdicke der Beschichtung. Dieser Fehler kann nur bei Gießprozessen beobachtet werden. Aufgrund der ungleichmäßigen Verteilung der Farbe auf der Leiterplatte, Es gab auch Mängel (völlige Abwesenheit der Farbe). Nicht abgedeckte Leiterzüge können Korrosion verursachen, die das elektrische Verhalten der Baugruppe beeinträchtigen kann.

Ursachen / Abhilfemaßnahmen:

Lackierprozess mangelhaft

Der gebrauchte Decklack ist nicht geeignet

Die Oberfläche des Grundmaterials ist nicht flach, die schlechte Verbreitung der Farbe

Defekte in der Beschichtung

Beschreibung:

Fehlfunktion der Farbe direkt auf einer Spur. Beim Löten, Es besteht die Gefahr, Brücken zwischen dem Lötauge und der benetzbaren Spurenoberfläche zu bauen. Dieses Phänomen ist hauptsächlich auf die Verunreinigungen der darunter liegenden Leiterplattenbereiche zurückzuführen. Nacharbeit ist erforderlich.

Ursachen / Abhilfemaßnahmen:

Verunreinigungen (Fette) der Leiterplatte

Fehler im Lackierprozess, die zu Teilfehlern führen

mechanische Einflüsse auf den Lack (Abfackeln der Farbe)

Risse

Beschreibung:

Risse (Mikrorisse) auf der Oberfläche der Lötstoppmaske. Fehler bei der Verarbeitung der Deckmaske (betont, Ausbeulung des Grundmaterials) Risse in der Lackoberfläche erzeugen. Das Hauptproblem ist das anschließende Eindringen von Feuchtigkeit aufgrund von Korrosion auf den Leiteroberflächen. Korrosion ist besonders problematisch für stromführende Leiter, da elektrische Wanderungen den Isolationswiderstand stark negativ beeinflussen.

Ursachen / Abhilfemaßnahmen:

Lötanschlagabdeckung defekt

mechanische Belastungen führen zu Lackrissen

Fehler beim Verarbeiten der Farbe

Risse in der Farbe

Beschreibung:

Die gleiche Verbindung wie oben, jedoch, Die Risse wurden hier mechanisch induziert, z.B.. durch Transporteinflüsse.

Ursachen / Abhilfemaßnahmen:

Unsachgemäße Handhabung der Leiterplatte / Baugruppe

Decklack nicht mechanisch beständig

Abteilungen, Falten

Beschreibung:

Abteilungen, Falten um zwei mit Lötmittel gefüllte Durchkontakte. Die thermische Belastung beim Löten, gepaart mit einem schlechten Layoutdesign (Die Farbe ist zu nahe am Durchkontakt), führte zu den gezeigten Farbentfernungen.