Erhöhen Sie die Integrationsdichte von PCB, indem Sie blinde Mikroben und Durchgangslöcher mit elektrolytischer Kupferabscheidung füllen.

Die fortschreitende Miniaturisierung elektronischer Schaltungen erfordert zunehmend die Verwendung von HDI-Leiterplatten mit kupfergefüllten blinden Mikrovias. Ein neu entwickelter Kupferelektrolyt, das derzeit unter produktionsbedingten Bedingungen getestet wird, ermöglicht das fehlerfreie Befüllen von blinden Mikrovias mit einer geringen Kupferschichtdicke auf der Leiterplattenoberfläche. Ein derzeit in der Entwicklung befindlicher Kupferelektrolyt sollte auch in Zukunft das zuverlässige Befüllen von Durchgangslöchern ermöglichen – Die aktuelle Entwicklungsarbeit zeigt bereits vielversprechende Ergebnisse.

Füllen von Blind Microvia und Durchgangslöchern

Erhöhung der Verpackungsdichte von Leiterplatten durch Auffüllen von blinden Durchkontaktierungen und Durchgangslöchern durch galvanische Abscheidung von Kupfer.

Die zunehmende Miniaturisierung elektronischer Schaltungen macht Gebrauch von HDI-Platine (HDI-Leiterplatten) mit kupfergefüllten blinden Mikro-Durchkontaktierungen, zunehmend wünschenswert. Ein neu entwickelter Kupferelektrolyt, Derzeit unter simulierten Produktionsbedingungen getestet, ermöglicht das fehlerfreie Füllen von blinden Durchkontaktierungen bei gleichzeitiger Reduzierung der Kupferablagerungsdicke auf der Plattenoberfläche. Dies bringt einen effizienteren Materialeinsatz und damit eine Reduzierung der Kosten für die Leiterplattenherstellung mit sich. Ein weiterer Kupferelektrolyt, der derzeit entwickelt wird, verspricht eine zuverlässige Befüllung der Durchgangslöcher.

1 Einführung

In der Mikroelektronik, Es gibt immer noch einen Trend zur Miniaturisierung, das ist, zu kleineren und leistungsstärkeren Systemen, die auch günstiger sein sollen als frühere Systeme. Die bekanntesten Beispiele hierfür sind Smartphones und Tablet-PCs, deren Leistung davon – trotz gleicher oder noch kleinerer Gerätegröße – hat in den letzten Jahren erheblich zugenommen.

HDI-Leiterplatten (HDI: Verbindung mit hoher Dichte) einen wesentlichen Beitrag zur Miniaturisierung leisten. Zum elektrischen Anschluss einzelner Leiterplattenschichten, platzsparende Sacklöcher (blinde Mikrovias) werden anstelle von Durchgangslöchern verwendet. Die Integrationsdichte kann weiter erhöht werden, indem die blinden Mikrovias mit elektrolytisch abgeschiedenem Kupfer gefüllt werden (blinde Microvia-Füllung). Inzwischen, Die Verwendung von HDI-Leiterplatten ist nicht mehr auf mobile Elektronik beschränkt, sondern wird zunehmend auch in anderen Anwendungen eingesetzt, zum Beispiel in der Automobilbranche.

Ein neu entwickelter Elektrolyt, Beim Blind Microvia Filling wird nur eine sehr geringe Kupferschichtdicke im Vergleich zur vorherigen Elektrolytgeneration abgeschieden, aktiviert die Ressource, Energie- und kosteneffiziente Herstellung von HDI-Leiterplatten.

Da die Integrationsdichte von HDI-Leiterplatten durch Verwendung sehr dünner Kernmaterialien noch weiter erhöht werden kann, die Entwicklung von Elektrolyten zum Füllen von Durchgangslöchern (Englisch: Durch Lochfüllung) wird derzeit verstärkt. Die Ergebnisse der Entwicklungsarbeit in diesem Bereich werden vorgestellt.

2 Miniaturisierung auf dem Gebiet der Mikroelektronik

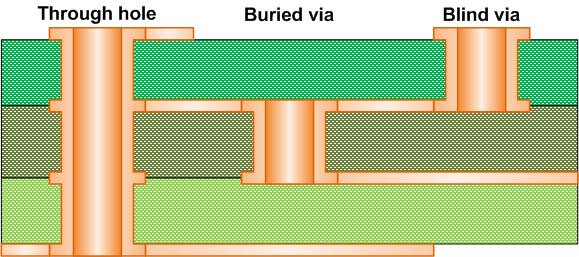

Die bekanntesten Vertreter der fortschreitenden Miniaturisierung in der Mikroelektronik sind sehr leistungsfähige mobile Geräte wie Smartphones und Tablets. Die hohen und stetig wachsenden Verkaufszahlen spiegeln die große Attraktivität dieser Geräte wider. Im 2013, mehr als 1 Milliarden Smartphones wurden zum ersten Mal verkauft, Verkäufe von rund 1.2 Milliarden werden in erwartet 2014 und herum 1.8 Milliarden in 2017 [2]. Im Bereich Tablet-PCs, Verkauf von 271 Millionen Geräte werden vorhergesagt 2014, das entspricht einem Anstieg von fast 40% verglichen mit dem vorherigen Jahr [3].

Diese werden in Prozessoren mit sehr kleinen Gehäusegrößen und einer sehr großen Anzahl von zunehmend netzartigen Anschlüssen installiert. Die Unterseite des Prozessors hat 976 Verbindungen auf einer Fläche von knapp unter 2 cm², Dies entspricht etwa fünf Verbindungen pro Quadratmillimeter. Die Tonhöhe der Verbindungen ist nur 400 um.

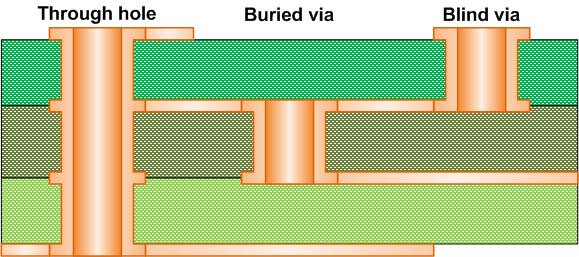

3 Miniaturisierung im Bereich Leiterplatten

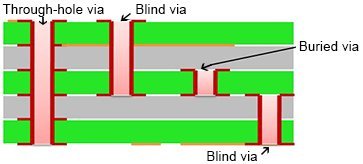

Für den platzsparenden und zuverlässigen elektrischen Anschluss von Prozessoren mit extrem hohen Anschlussdichten sind Leiterplatten mit entsprechend hoher Integrationsdichte erforderlich. Die klassische mehrschichtige Leiterplatte ist dafür ungeeignet, jedoch, da es Durchgangslöcher für die elektrische Verbindung einzelner Leiterplattenschichten verwendet. Diese haben relativ große Durchmesser und, da sie erst nach dem Pressen der einzelnen Schichten gebohrt werden, Sie erstrecken sich über die gesamte Leiterplattendicke. Dies hat zur Folge, dass auch wenn direkt benachbarte Schichten verbunden sind, Der Raum über und unter der eigentlichen Verbindung geht verloren und kann daher nicht für andere Strukturen verwendet werden, zum Beispiel Dirigentenbahnen. Die daraus resultierende geringe Integrationsdichte von Mehrschichtplatinen reicht für die oben beschriebenen Anforderungen nicht aus.

Vor einigen Jahren, eine neue, hochintegrierte Erzeugung von Leiterplatten, die sogenannte HDI-Platine, wurde daher entwickelt, die ursprünglich hauptsächlich für die Herstellung von Mobiltelefonen verwendet wurde. Bei der Herstellung von HDI-Leiterplatten, Die einzelnen Leiterplattenschichten werden nacheinander aufgebaut (SBU, Sequentieller Aufbau). Die elektrische Verbindung benachbarter Montagepositionen erfolgt mit lasergebohrten Blindmikrovias. Zahl 2 zeigt schematisch die Struktur von a 2-4-2 HDI-Platine, d.h.. Die Leiterplatte besteht aus einem vierschichtigen Mehrschichtkern und zwei Schichten auf jeder Seite.

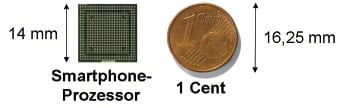

4 Blinde Mikrovia

Im Vergleich zu Durchgangslöchern, blinde Mikrovias haben kleinere Durchmesser im Bereich von 50 .m zu 150 µm und sie erstrecken sich nur in z-Richtung über die Dicke einer Einbaulage (typischerweise 50 .m zu 150 um). Sie nehmen nur so viel Platz ein, wie für die eigentliche Verbindung tatsächlich benötigt wird. HDI-Leiterplatten haben somit eine viel höhere Integrationsdichte als mehrschichtige Leiterplatten und eignen sich daher zur Signalentbündelung hochfunktioneller elektronischer Bauteile auf kleinstem Raum.

4.1 Blindes Microvia füllen

Eine weitere Erhöhung der Integrationsdichte ermöglicht gestapelte blinde Mikrovias (gestapelte blinde Mikrovias). Wenn elektrolytisch abgeschiedenes Kupfer anstelle von leitfähiger Paste zum Befüllen verwendet wird, Dies führt zu folgenden weiteren Vorteilen:

Erhöhte Zuverlässigkeit (Die blinden Mikrovias enthalten nur Kupfer, Es gibt keine zusätzliche Schnittstelle)

besseres Wärmemanagement (Wärmeverlust kann über die hoch wärmeleitende abgeleitet werden, kupfergefüllte blinde Mikrovias)

Weitere Erhöhung der Integrationsdichte (Keine zusätzlichen Pads (Pads) werden auf der Leiterplattenoberfläche zum Kontaktieren von Bauteilen benötigt)

Die Hauptprozessschritte bei der Herstellung von HDI-Leiterplatten mit kupfergefüllten Blindmikrovias sind in Abbildung schematisch dargestellt 4. Wenn eine weitere Schicht aufgebaut werden soll, Die Prozesssequenz muss beginnend mit dem Prozessschritt erneut durchlaufen werden 2.

Durch das Übereinanderstapeln von kupfergefüllten Blindmikrovias können auch nicht benachbarte Montagepositionen mit minimalem Platzbedarf elektrisch leitend verbunden werden (Feige. 5). Die Verwendung von Pad-In-Via- oder Via-In-Pad-Designs führt zu einer weiteren Erhöhung der Integrationsdichte, da Komponentenverbindungen direkt auf die kupfergefüllten Blindmikrovias gelötet werden können, damit sind keine zusätzlichen Anschlussflächen erforderlich (Feige. 6).

4.2 Bisherige Elektrolyte für die blinde Mikrovia-Füllung

Typischerweise, Elektrolyte für die blinde Mikrovia-Füllung enthalten eine relativ hohe Konzentration an Kupferionen im Bereich von 40 G / Ich zu 60 G / l in Kombination mit einer niedrigen Schwefelsäurekonzentration im Bereich von 10 ml / Ich zu 50 ml / l sowie Chloridionen. Die zur Kontrolle der Beschichtungseigenschaften erforderlichen organischen Elektrolytadditive unterscheiden sich von Fachunternehmen zu Fachunternehmen, In den Elektrolytadditiven sind jedoch meist die folgenden drei Komponenten enthalten:

Grundadditiv (Inhibitor)

Getreideveredler (Aktivator)

Richtmaschine (Inhibitor)

Zusätzlich, Die Methoden der verschiedenen Anbieter können sich auch in den folgenden Funktionen unterscheiden:

Systemtechnik (Standard vertikales System, vertikales kontinuierliches System, horizontales durchgehendes System)

Anodentyp (Kupferanode, unlösliche Anode)

Aktuelle Form (Gleichstrom, Pulsstrom, Sperrimpulsstrom)

anwendbare Stromdichte

Die bisher von Schlötter angebotenen Methoden zur blinden Mikrovia-Befüllung arbeiten ausschließlich mit Gleichstrom in vertikalen Standardsystemen oder vertikalen kontinuierlichen Systemen.

In den frühen Jahren der blinden Mikrovia-Füllung, Zusätzlich zu den Standardanforderungen für elektrolytisch abgeschiedene Kupferbeschichtungen für Leiterplatten gab es im Wesentlichen die folgenden zusätzlichen Anforderungen (z.B.. Duktilität, Verlässlichkeit):

fehlerfreie Befüllung der blinden Mikrovias ohne Elektrolyteinschlüsse

Minimaler Füllstand oder maximal zulässige Vertiefung (Delle.

Während des Füllvorgangs, 93 µm Kupfer (B.) wurde in der blinden Mikrovia abgelagert, während die Schichtdicke auf der Oberfläche nur ist 22 um (C.), Daraus ergeben sich folgende Kennzahlen:

Vertiefung (A-B): 30.4 um

Füllgrad (B. / EIN): 75%

Metallverteilung (B. / C.): 426%

Dies liegt hauptsächlich an der Wirkungsweise der Richtmaschine, wodurch sich das Kupfer nicht auf der Oberfläche, sondern in den blinden Mikrovias ablagert, d.h.. in den Bereichen niedrige Stromdichte und geringer Elektrolytaustausch.

Um ein gutes Füllergebnis zu erzielen, Die Elektrolytadditive müssen sehr gut aufeinander abgestimmt sein. Abbildung 8a zeigt eine blinde Mikrovia vor dem Füllvorgang sowie unterschiedliche Ergebnisse, Dies kann nur durch Variation der Elektrolytadditive geschehen – mit ansonsten gleichen Trennparametern (Feige. 8Sein).

4.3 Neuer Elektrolyt für die blinde Mikrovia-Füllung

Die Integrationsdichte der Leiterplatten kann durch Verringern der Spurbreite und des Abstands noch weiter erhöht werden. Zum Ätzen solcher Feinleiter, jedoch, Die Kupferschichtdicke auf der Oberfläche muss gering sein, da sonst starke Hinterschneidungen und Probleme mit dem Leiterquerschnitt auftreten können.

Wie in Abbildung gezeigt 4, Die Kupferschichtdicke kann nach dem Befüllen reduziert werden – möglicherweise wiederholt – Kupferverdünnung, Hierfür sind jedoch zusätzliche Prozessschritte und Systeme erforderlich. Zusätzlich, Die Kupferverdünnung von zuvor abgeschiedenem Kupfer wird teilweise entfernt, was sich negativ auf die Ressource auswirkt, Energie- und Kosteneffizienz bei der Herstellung von Leiterplatten. Um dies vollständig zu vermeiden – oder zumindest zu reduzieren – die Kupferverdünnung, zusätzlich zu den bereits genannten Anforderungen, Das Erfordernis, während des Füllprozesses die kleinstmögliche Kupferschichtdicke abzuscheiden, wurde in den letzten Jahren hinzugefügt.

50-70 mg / l Chlorid

3–10 ml / l zusätzliche Slotocoup SF 31

0.2–1,0 ml / l zusätzliche Slotocoup SF 32

0.2–2,0 ml / l zusätzliche Slotocoup SF 33

Der Elektrolyt wird bei Stromdichten von maximal betrieben 2 EIN / dm² im Temperaturbereich zwischen 18 ° C und 22 ° C..

Im Vergleich zur vorherigen Elektrolytgeneration, Die auf der Oberfläche abgelagerte Kupferschichtdicke könnte extrem reduziert werden. Dies zeigt die Metallverteilung, was im gezeigten Labortest einen extrem hohen Wert von über hat 2000% (Feige. 9b).

SF-Steckplatz 30 wird derzeit in Zusammenarbeit mit dem taiwanesischen Schlötter-Partner AGES im PCB Development Center in Taipeh getestet, das in eröffnet wurde 2012 unter produktionsbedingten Bedingungen in a 7200 Liter vertikales kontinuierliches System (Feige. 10).

Vertiefung: 7.0 um

Füllgrad: 91%

Metallverteilung: 740%

Abbildung 11b zeigt eine weitere kupfergefüllte Blind Microvia, Dies kommt von derselben Platine wie der Blind Microvia in Abbildung 11a. Es ist bemerkenswert, dass, trotz der nicht optimalen BMV-Geometrie, Das Füllergebnis ist sehr gut.

Slotocup SF 30 ermöglicht auch das fehlerfreie Füllen eng beieinander liegender blinder Mikrovias mit geringer Schichtdicke der Kupferoberflächen.Abb. 12: SF-Steckplatz 30 Testergebnisse beim Füllen eng beieinander liegender blinder Mikrovias

Sehr flachblinde Mikrovias, die sich ergeben, wenn extrem dünne Dielektrika verwendet werden, kann auch fehlerfrei mit dem neuen Elektrolyten gefüllt werden, Dies führt jedoch zu etwas höheren Kupferschichtdicken.

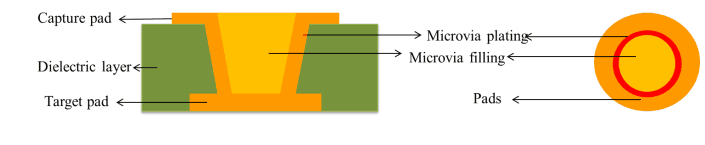

5 Durchgangslochfüllung

Eine weitere Erhöhung der Integrationsdichte von HDI-Leiterplatten kann erreicht werden, indem die bisher verwendeten relativ dicken Mehrschichtkerne durch deutlich dünnere Kerne mit dazwischen liegenden Dicken ersetzt werden 100 µm und 200 um.

Sehr dünne Kerne können auch Durchgangslöcher anstelle von blinden Mikrovias aufweisen. Vorher, Diese Durchgangslöcher wurden zuerst nach der ersten Kupferbeschichtung mit Paste gefüllt und dann erneut verkupfert, um die Pads herzustellen. Zusätzlich, Die Verwendung von Paste kann zu Zuverlässigkeitsproblemen führen.

5.1 Neue Elektrolyte zum Durchfüllen von Durchgangslöchern

Anfänglich, Es wurde versucht, die bereits in der blinden Mikrovia-Füllung im Bereich der Durchgangslochfüllung bewährten Kupferelektrolyte zu verwenden. jedoch, Es wurde gezeigt, dass diese Elektrolyte für diese Anwendung nicht geeignet sind, so dass weitere Entwicklungsarbeiten erforderlich waren. Einige Laborergebnisse aus der aktuellen Entwicklungsarbeit sind in Abbildung dargestellt 16.

Durch Modifizieren der Elektrolytzusammensetzung, Das Füllen von Durchgangslöchern konnte deutlich verbessert werden (ca.. 85 µm Bohrlochdurchmesser / ca.. 110 µm Bohrlochtiefe). Alle vier in Abbildung gezeigten Ablagerungen 16 wurden jeweils mit Gleichstrom bei gleicher Abscheidezeit und Stromdichte durchgeführt. Zusätzlich, Während der gesamten Abscheidungsperiode wurde nur ein Elektrolyt abgeschieden, d.h.. es gab keine Elektrolytänderung im Verlauf der Abscheidung.

Mit zunehmendem Seitenverhältnis, d.h.. abnehmender Bohrlochdurchmesser und / oder Erhöhung der Bohrlochtiefe, Der Massentransport und damit die anschließende Abgabe von Kupferionen wird erschwert. Als Ergebnis, Das fehlerfreie Befüllen der Durchgangslöcher ohne Elektrolyteinschlüsse wird immer schwieriger. Zahl 17 zeigt zwei Füllergebnisse von nicht vorverstärkten Durchgangslöchern (ca.. 50 µm Bohrlochdurchmesser / ca.. 160 µm Bohrlochtiefe).

Der im Defekt eingeschlossene Elektrolyt (Feige. 17ein) dehnt sich aus, wenn die HDI-Leiterplatte erwärmt wird und kann daher bereits beim Löten von Bauteilen oder bei anschließender Temperaturerhöhung zu einem Riss in dieser Verbindung führen, Dies kann zu einem Systemausfall führen. Der Schwerpunkt der aktuellen Entwicklungsarbeit liegt auf, deshalb, das zuverlässig fehlerfreie Füllen von Durchgangslöchern mit unterschiedlichen Seitenverhältnissen.

6 Abschließend

Aufgrund ihrer hohen Integrationsdichte, HDI-Leiterplatten ermöglichen eine zuverlässige Entflechtung der hohen Anschlussdichten dieser Mikroprozessoren auf kleinstem Raum.

Durch Füllen von blinden Mikro-Durchkontaktierungen mit elektrolytisch abgeschiedenem Kupfer, Die Integrationsdichte von HDI-Leiterplatten kann weiter erhöht werden. Der neu entwickelte Elektrolyt Slotocoup SF 30, das derzeit in Taiwan unter produktionsbedingten Bedingungen getestet wird, ermöglicht fehlerfreies Füllen mit geringer Kupferschichtdicke. Dies führt zu einer weiteren Erhöhung der Integrationsdichte und zu einer größeren Ressource, Energie- und kosteneffiziente Herstellung von HDI-Leiterplatten. Die erste Installation bei einem Kunden ist für das zweite Quartal geplant 2014.

Die Integrationsdichte kann durch sogenannte kernlose Strukturen noch weiter erhöht werden, die aus sehr dünnen Kernmaterialien bestehen. Die Ergebnisse der aktuellen Entwicklungsarbeiten zeigen, dass die Gleichstromabscheidung von Kupfer es grundsätzlich ermöglicht, die Durchgangslöcher in diesen Kernen zu füllen. Da das Füllergebnis und damit die Qualität der Verbindung vom Seitenverhältnis der Durchgangslöcher abhängt, Die Realisierung einer zuverlässigen fehlerfreien Füllung mit unterschiedlichen Seitenverhältnissen steht derzeit im Vordergrund der Entwicklungsarbeit.